Introduction: Unveiling The Essence Of The Instruction Cycle

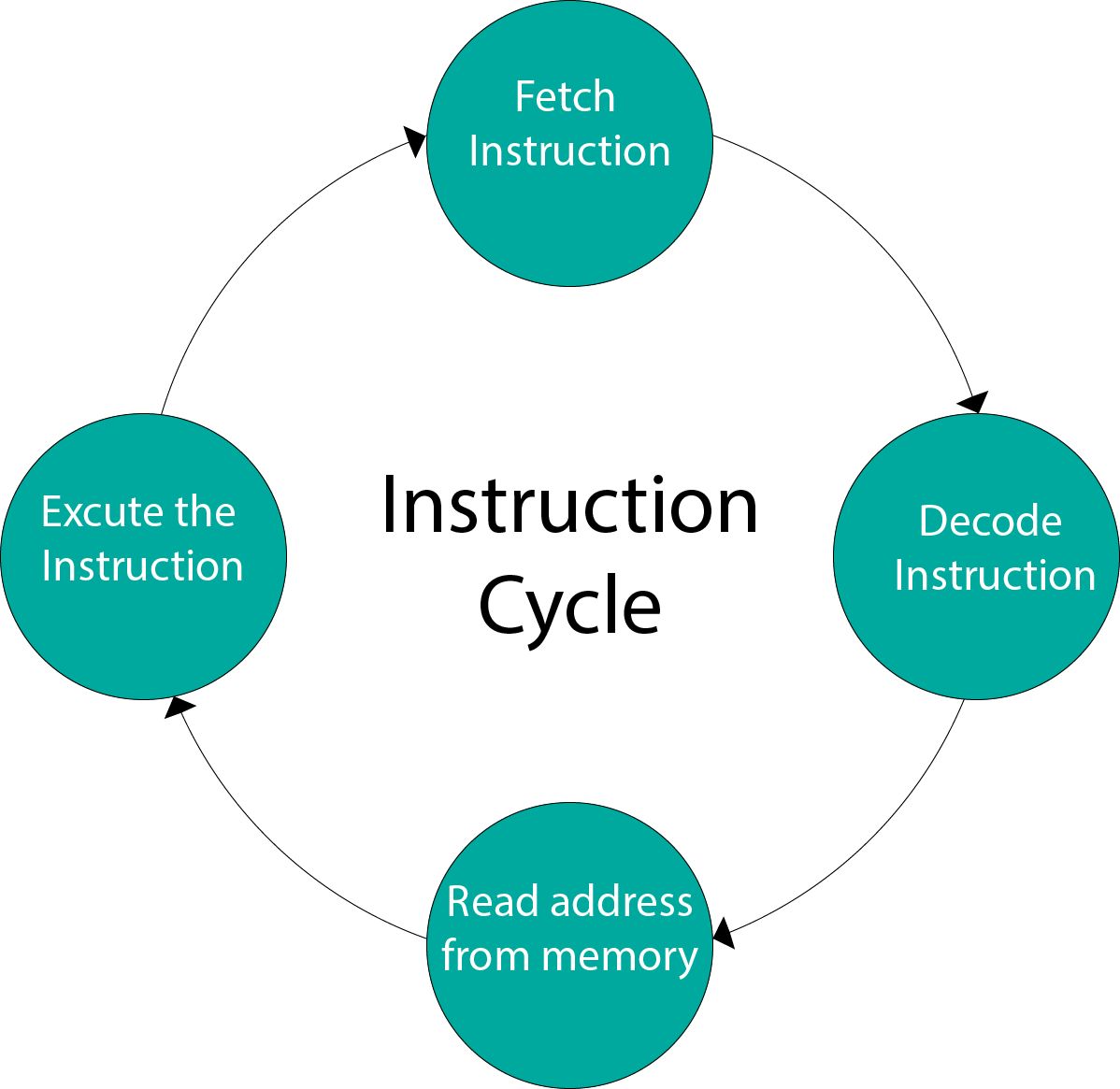

The instruction cycle (also known as the fetch–decode–execute cycle, or simply the fetch-execute cycle) is the cycle that the central processing unit (CPU) follows from boot-up until the computer has shut down in order to process instructions. It is composed of three main stages: the fetch stage, the decode stage, and the execute stage.

- PC – Program counter

- MAR – Memory address register

- MDR – Memory data register

- CIR – Current instruction register

- CU – Control unit

- ALU – Arithmetic logic unit

In simpler CPUs, the instruction cycle is executed sequentially, each instruction being processed before the next one is started. In most modern CPUs, the instruction cycles are instead executed concurrently, and often in parallel, through an instruction pipeline: the next instruction starts being processed before the previous instruction has finished, which is possible because the cycle is broken up into separate steps.[1]

In The Realm Of Computer Architecture And Processing, The Instruction Cycle Stands As A Fundamental Concept, Orchestrating The Execution Of Instructions Within A Computer’s Central Processing Unit (CPU). This Guide Navigates Through The Intricacies Of The Instruction Cycle, Elucidating Its Stages, Significance, And The Seamless Orchestration Of Operations That Drive Computing Functionality.

The Foundation: Understanding The Instruction Cycle

Definition And Purpose*

The Instruction Cycle, Often Referred To As The Fetch-Decode-Execute Cycle, Serves As The Cornerstone Of Computer Processing. Its Primary Purpose Is To Systematically Execute Machine-Level Instructions, Transforming High-Level Programming Commands Into Actions Performed By The CPU.

Role In Computer Processing*

At Its Core, The Instruction Cycle Facilitates Communication Between The CPU And Memory, Ensuring That Instructions Are Retrieved, Interpreted, And Executed In A Sequence That Enables The Computer To Perform Desired Tasks. It Forms The Foundation Of The Execution Of Programs And Processes Within A Computing System.

Stages Of The Instruction Cycle

Fetch: Retrieving Instructions*

The Cycle Initiates With The Fetch Stage, Where The CPU Fetches The Next Instruction From The Computer’s Memory. The Program Counter, A Vital Component, Determines The Memory Location Of The Next Instruction To Be Executed. This Stage Ensures A Continuous Flow Of Instructions Into The CPU.

Decode: Interpreting Instructions*

Once Fetched, Instructions Move To The Decode Stage, Where The CPU Interprets Their Meaning. The Opcode, Or Operation Code, Is Extracted, Indicating The Specific Operation The CPU Must Perform. Additional Data Or Operands Associated With The Instruction Are Also Identified During This Stage.

Execute: Carrying Out Operations*

The Heart Of The Cycle Lies In The Execute Stage, Where The CPU Performs The Actual Operations Dictated By The Decoded Instructions. This Could Involve Arithmetic Calculations, Logical Operations, Data Manipulation, Or Other Tasks As Specified By The Interpreted Instructions.

Write Back: Updating Memory Or Registers*

Upon Completing The Execution, The Results Are Written Back To Memory Or Registers, Finalizing The Instruction Cycle. This Stage Ensures That Any Changes Or Outcomes Of The Executed Instruction Are Appropriately Stored, Facilitating Continuity In Program Execution.

The Synchronization Dance: Coordination With The System Clock

System Clock’s Pivotal Role*

The Instruction Cycle Is Intricately Tied To The System Clock, A Pulsating Heartbeat That Synchronizes The Operations Of The CPU. Each Stage Of The Instruction Cycle Aligns With A Clock Cycle, Creating A Rhythmic Coordination That Dictates The Pace At Which Instructions Are Processed.

Clock Speed And Performance*

The Speed Of The System Clock, Measured In Hertz, Directly Influences The Performance Of The CPU. A Higher Clock Speed Allows For More Instructions To Be Processed In A Given Time Frame, Enhancing The Overall Computational Capabilities Of The System.

Von Neumann Architecture: The Instruction Cycle’s Home

Architectural Foundation*

The Instruction Cycle Finds Its Home In The Von Neumann Architecture, A Fundamental Design Framework For Modern Computers. This Architecture Integrates The CPU, Memory, And Input/Output Components, Creating A Cohesive Structure That Enables The Seamless Execution Of The Instruction Cycle.

The Harvard Architecture Distinction*

While The Von Neumann Architecture Is Prevalent, The Harvard Architecture Presents An Alternative. Distinguishing Itself By Using Separate Memory Spaces For Instructions And Data, The Harvard Architecture Alters The Way The Instruction Cycle Interacts With Memory, Potentially Impacting System Performance.

Pipeline Processing: Streamlining Operations

Parallel Execution Through Pipelining*

To Enhance Efficiency, Modern Cpus Often Employ Pipeline Processing, A Technique That Allows Multiple Instructions To Progress Through Different Stages Of The Instruction Cycle Simultaneously. This Parallel Execution Minimizes Idle Time And Optimizes The Use Of CPU Resources.

Potential Challenges And Hazards*

While Pipeline Processing Improves Throughput, It Introduces Challenges Such As Data Hazards, Control Hazards, And Structural Hazards. Managing These Hazards Requires Sophisticated Techniques, Including Forwarding, Stalling, And Branch Prediction, To Ensure The Seamless Flow Of Instructions In The Pipeline.

Real-World Applications: Instruction Cycle In Action

Application To Programming Languages*

Understanding The Instruction Cycle Is Pivotal For Programmers. High-Level Programming Languages Are Translated Into Machine Code, A Series Of Instructions That Undergo The Instruction Cycle To Be Executed By The CPU. This Translation Ensures That The Intended Operations Are Carried Out Accurately.

Operating System Interaction*

Operating Systems Serve As Orchestrators, Managing The Execution Of Programs And Processes. The Instruction Cycle, In Conjunction With The Operating System, Governs How Instructions Are Scheduled, Prioritized, And Executed, Contributing To The Overall Functionality Of The Computing Environment.

Challenges And Advancements: Pushing The Boundaries

Challenges In Instruction Cycle Optimization*

Optimizing The Instruction Cycle Faces Challenges, Including Minimizing Latency, Managing Dependencies Between Instructions, And Addressing The Complexities Introduced By Conditional Branches. Overcoming These Challenges Requires Innovative Approaches In Processor Design And Architecture.

Advancements In Microarchitecture*

Ongoing Advancements In Microarchitecture, Including Superscalar And Out-Of-Order Execution, Push The Boundaries Of Instruction Cycle Optimization. These Approaches Allow Multiple Instructions To Be Processed Concurrently And Out Of Sequence, Maximizing CPU Utilization And Performance.

The Future Horizon: Evolving Instruction Processing

Quantum Computing Paradigm*

As The Computing Landscape Evolves, Quantum Computing Emerges On The Horizon. Quantum Computers, With Their Unique Processing Model Based On Qubits, Challenge The Traditional Instruction Cycle. Understanding The Instruction Cycle In The Quantum Computing Paradigm Involves Embracing Concepts Such As Superposition And Entanglement.

Neuromorphic Computing Influence*

Neuromorphic Computing, Inspired By The Human Brain’s Neural Architecture, Introduces A Paradigm Shift In Information Processing. The Instruction Cycle In Neuromorphic Systems Is Characterized By Neural Networks And Parallel Processing, Revolutionizing How Computations Are Performed.

Conclusion: The Pervasive Influence Of The Instruction Cycle

In Conclusion, The Instruction Cycle Serves As The Beating Heart Of Computer Processing, Orchestrating The Execution Of Instructions With Precision And Rhythm. From Its Foundational Stages Of Fetch To The Final Write Back, The Cycle Seamlessly Integrates With The System Clock, Dances Within The Von Neumann Architecture, And Adapts To Advancements In Pipeline Processing And Microarchitecture. As Technology Continues To Evolve, The Instruction Cycle Remains A Pervasive And Essential Concept, Shaping The Present And Future Landscape Of Computing.